Делители частоты на «нестандартное» число

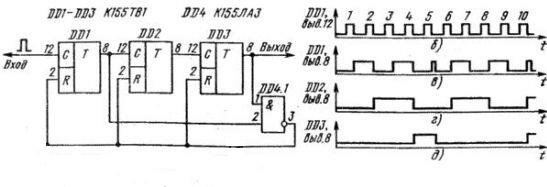

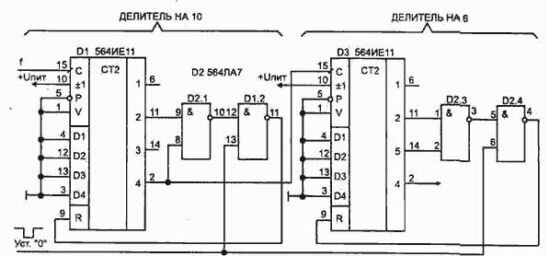

Для деления частоты на 2, 4, 8, 16 и т.д. достаточно организовать цепочку, состоящую из нужного числа счетных, так называемых, D-триггеров. Для деления частоты в «нестандартное» число раз, к примеру, на 3 или 5, необходима специальная схема контроля, которая бы сбрасывала все триггеры при определенном их состоянии, чтобы счет начинался с нуля. Взглянем на схему ниже.

Благодаря элементу 3И-НЕ при состоянии триггеров 1-0-1 низкий уровень, появившийся на его выходе, сбросит все триггеры в ноль (входы R), и счетчик начнет считать сначала. Если перевести 101 в более привычную для нас десятичную систему счисления, получим 5, и это значит, что наш счетчик будет обнуляться после каждого пятого импульса. К нашим услугам делитель на 5.

Аналогичным образом можно организовать деление на любое число – вопрос лишь в количестве D-триггеров и сложности схемы управления. Впрочем, чтобы построить нечетный делитель до 10 (а точнее на 3, 5, 6, 7, 10) можно обойтись достаточно простой системой контроля, состоящей лишь из… одного конденсатора:

Делитель на 5 с использованием в схеме сброса конденсатора

Фокус этой схемы в том, что первый и второй триггеры сбросятся в тот момент, когда на инверсном выводе третьего произойдет переход с высокого логического уровня на низкий. Если вы разобрались в работе D-триггера, которую я описывал в предыдущих статьях, то без труда определите, что мы организовали все тот же счетчик-делитель на 5, но схема его гораздо проще рассмотренного выше.

Аналогично организуем счетчик-делитель на 3:

Обратите внимание на схему делителя на 6 — это тот же делитель на 3, перед которым стоит обычный счетный триггер-делитель на 2 (DD6). Ну а делитель на 10 — это делитель на 2 + делитель на 5. Несмотря на свою простоту, такие схемы при использовании микросхем ТТЛ применяются достаточно широко и вполне надежны.

Источник

Делители частоты на D-триггерах

В статьях о D-триггере с динамической синхронизацией (далее в статье – просто «триггер») я упоминал о том, что он может использоваться в качестве делителя частоты. Сегодня мы рассмотрим, каким образом это можно сделать. Итак, в нашем распоряжении микросхема К555ТМ2, которая содержит, как я уже говорил, 2 триггера, причем каждый имеет инверсные входы принудительной установки и сброса. Попробуем включить один триггер следующим образом:

В исходном состоянии на прямом выходе схемы «0», на инверсном «1», значит и на входе D тоже «1». Подаем на вход С высокий уровень. Единичка со входа переписывается в триггер, но на выходе еще не появляется (вспоминаем как работает такой тип триггера). Снимаем высокий уровень со входа С – единичка появилась на прямом выходе, а значит на инверсном (и на входе D) установился ноль. Снова включаем синхронизацию и снова данные (на этот раз «0») записываются в триггер, но не появятся на выходе до тех пор, пока сигнал синхронизации не будет снят. На прямом выходе «0», на входе данных снова «1». Цикл деления закончится и выглядит он следующим образом:

На графике хорошо видно, что на выходе уровень меняется в два раза реже, чем на входе синхронизации, и если циклы повторять, то частота повторения единичек на выходе триггера будет в два раза ниже частоты импульсов синхронизации:

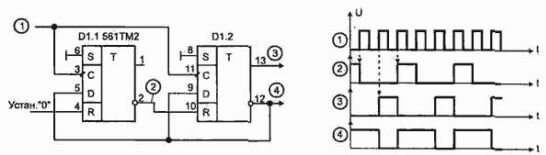

Если необходимо еще уменьшить частоту, то сигнал с выхода первого триггера можно подать на вход синхронизации следующего и разделить его еще в 2 раза, что мы и сделаем, использовав микросхему К555ТМ2:

Как видите, используя всего один корпус микросхемы, мы построили делитель на 4, причем выводы принудительной установки триггеров нам не понадобились и мы оставили их свободными.

Таким образом, увеличивая количество триггеров или, как говорят, наращивая разрядность, можно разделить частоту на 2, 4, 8, 16 и т.д. А как быть, если потребуется деление, скажем, на 3 или 6? Можно построить и такой делитель, но для этого нам придется разобраться со счетчиками и получить представление о двоичном счислении, чем мы и займемся на следующих занятиях.

Источник

Делители частоты на микросхемах ТТЛ и КМОП

Сразу оговорюсь, что схемотехника построения делителей частоты на ТТЛ и КМОП практически ничем не отличается (единственным отличием может быть существование того или иного счетчика в каждой из серий). Таким образом схемы, приведенные в статье, могут быть использованы для построения делителей как на КМОП, так и на ТТЛ логике.

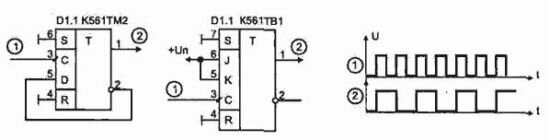

Проще и нагляднее всего реализовать делитель частоты с помощью счетных триггеров (D-триггеров). Именно такие триггеры являются основой для построения счетчиков. Они работают в широком диапазоне частот (от 0 до граничной частоты переключения элементов серии), достаточно помехоустойчивы, не требуют дополнительных навесных элементов и просты в повторении. Еще один вариант – использование в качестве делителя JK-триггер. Поскольку такой триггер поистине универсальный, его несложно включить в счетном режиме. Ниже представлено две схемы-делителя на 2. Один из них собран на счетном триггере (1 элемент микросхемы ТМ2), второй на JK-триггере (рис.1).

Рис.1. Делитель на D и JK триггере

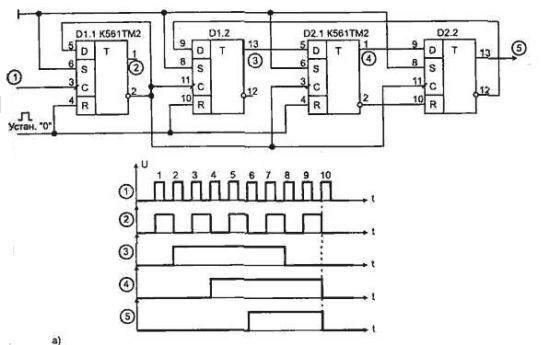

Соединив несколько делителей на 2 можно получить линейку с выходными частотами f/2, f/4, f/8, f/16 (выходы Q1, Q2, Q3, Q4 соответственно (рис.2).

Поскольку в одном корпусе ТМ2 находится 2 D-триггера, то на одной микросхеме несложно собрать делитель частоты на 3 (рис.3).

Для построения делителя на 5 на JK-триггерах в схему придется добавить логический элемент 2И-НЕ (рис.4).

Еще один корпус ТМ2 понадобится чтобы построить делитель частоты на 10 (рис.5).

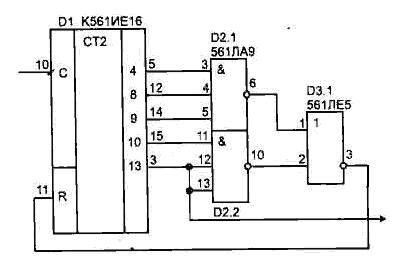

Для большего коэффициента деления удобнее использовать микросхемы счетчиков:

Делитель на 1000

Особый интерес представляет микросхема серии ТТЛ – К155ИЕ2. Состоит она из двух блоков — делителя на 2 (вход С1) и делителя на 5 (C2). При соединении выхода первого делителя (вывод 12) с входом второго, легко получить делитель на 10 (рис.6 а). Еще один полезный узел микросхемы — 2 входа сброса, соединенных по «И» (выводы 2,3). Благодаря этому узлу и выводам выхода с каждого триггера счетчика (выводы 12,9,8,11) несложно собрать делитель с числом от 2 до 10 без использования дополнительных элементов. Для примера на рисунке 6 б изображен делитель на 6, а на рис. 6 в – делитель на 8.

Источник

Схемы делителей частоты

Схема пробника-делителя частоты для частотомера.

Схема пробника-делителя ( Рис.1 ) хорошо подходит для измерения высокочастотных сигналов в схемах, где требуется малое вмешательство из-за возможного ухода частоты. Предлагаемый пробник-делитель к частотомеру предназначен для измерения частоты в диапазоне 60 – 2300 МГц. Входной сигнал через ФВЧ С2L1 с частотой среза Fc = 55 МГц поступает на вход СВЧ усилителя на VT1. Его исток заземлён по переменному току конденсаторами С7, С8.

Диоды VD1, VD2 защищают вход VT1 от перегрузки по напряжению. Усиленный сигнал подаётся на первый счётчик-делитель DD1 (коэффициент деления 4), второй делитель DD2 (4) и на третий делитель DD 3 (10). Далее сигнал через преобразователь ЭСЛ/ТТЛ на транзисторах VT2, VT3 поступает на выход (ХР2).

Катушка L1 – бескаркасная, имеет 8 витков провода ПЭВ-2 диаметром 0,5 мм и наматывается на оправке 5 мм. В качестве DD2 можно применить микросхему К193ИЕ7. Если в качестве DD1 использовать К193ИЕ5, верхний диапазон измеряемых частот снизится до 1,5 – 1,7 ГГц.

Отдельные экземпляры ИМС К193ИЕ7 устойчиво работают на частотах 2,7 – 2,9 ГГц. Делитель выполнен поверхностным монтажом и заключён в латунный экран, однако возможно применение обычного монтажа. При использовании фольгированного текстолита (е = 4,7) ширина печатных дорожек входных сигнальных цепей (сток-исток VT1, вход DD1) должна быть примерно 1,5 мм, а для фольгированного фторопласта (е = 2,9) – 3 мм (при толщине материала подложки 1 мм).

Делитель рассчитан на низкоомную нагрузку и имеет низкое входное сопротивление (50 ом). Для измерения сигналов высокоомных источников элементы R1, R2, C1, VD1, VD2 необходимо исключить, а ёмкость С2 – уменьшить до 1 пФ. При этом во избежание пробоя VT1 не рекомендуется измерять СВЧ колебания большой амплитуды. Делитель для удобства работы можно оснастить съёмными низкоомным и высокоомным зондами.

Данная схема хорошо демонстрирует построение высокочастотного делителя. В ней можно применять в качестве первых делителей микросхемы:

*К193ИЕ5 ( на 4 с максимальной частотой 1 – 1,5 ГГц );

SP8610 ( на 4 предел 1 ГГц );

*К193ИЕ7 ( на 4 предел 2 – 2,5 ГГц );

*К193ИЕ2 ( на 10 предел 500 МГц );

*SP8685 ( на 10 предел 600 МГц ).

В качестве последующих делителей могут быть применены следующие микросхемы:

К500ИЕ137 ( на 10 предел 125 МГц );

К500ИЕ136 ( на 16 предел 125 МГц );

К531ИЕ14 ( на 10 предел 80 МГц ).

Их следует компоновать для получения требуемого коэффициента деления и максимальной частоты счёта. Только необходимо при соединении каскадов на ЭСЛ микросхемах с каскадами на ТТЛ и КМОП после ЭСЛ включить буферный каскад, подобный каскаду на VT2 ( Рис.1 ) для согласования логических уровней.

Схема высококачественного пробника-делителя.

Ещё лучшим вариантом для высокочастотного делителя будет применение специализированной микросхемы фирмы Phillips SAB 6456 ( Рис.2 ).

Этот делитель имеет следующие параметры:

* коэффициент деления …. 64/256;

* напряжение питания .…. 4,5 – 5,5В;

* ток потребления … 21 мА;

* входная частота … 70 – 1000 МГц;

* чувствительность … 1 В;

Если оставить вывод 5 микросхемы SAB6456 свободным, её коэффициент деления будет 64, при заземлённом выводе – 256.

Делитель обладает очень высокой чувствительностью, частотомер с этим делителем можно также использовать как индикатор частоты для обнаружения ВЧ передатчиков, принимая сигнал на телескопическую антенну.

В. Г. Белолапотков, А. П. Семьян «500 схем для радиолюбителей ШПИОНСКИЕ ШТУЧКИ И НЕ ТОЛЬКО» Наука и техника, Санкт-Петербург, 2007г, стр. 240 – 243.

Источник

Записки программиста

Самодельный делитель/сумматор на 1-30 МГц

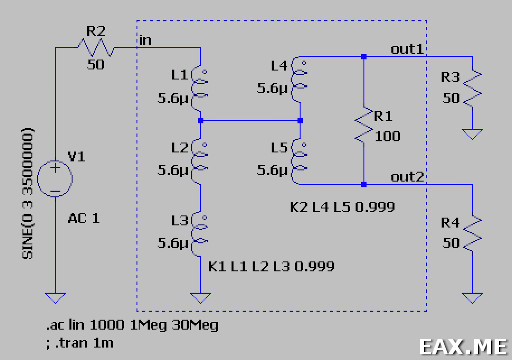

Порой бывает нужно взять ВЧ сигнал и разделить его на два одинаковых сигнала меньшей мощности. Устройство, решающее эту задачу, называется делитель мощности (power splitter). Некоторые делители также могут быть использованы и для обратной задачи. Тогда говорят, что устройство играет роль сумматора (power combiner). Сегодня мы рассмотрим схему делителя/сумматора на частоты 1-30 МГц и проверим, как она работает на практике.

Теория

Давайте разберемся, как это работает.

Резисторы R2-R4 просто показывают, что вход и выходы имеют импеданс 50 Ом. В самом делителе их нет. Итого остается два трансформатора, L1-L3 и L4-L5, а также резистор R1. Для начала рассмотрим работу устройства в режиме делителя.

Первый трансформатор нужен для согласования импеданса. Источник имеет импеданс 50 Ом. Выходы также имеют импеданс 50 Ом, но они соединены параллельно. Как мы скоро убедимся, наличие на выходе L4-L5 и R1 ни на что не влияет. Таким образом, нужно согласовать 50 Ом в 25 Ом. Можно заметить, что L1-L3 является автотрансформатором с отношением числа витков первичной и вторичной обмотки 3:2. То есть, он согласует входные 50 Ом в 50*(2/3) 2 или примерно 22.2 Ом. Это не ровно 25 Ом, но достаточно близко (КСВ 1.126, 0.35% отраженной мощности).

В обмотках L4-L5 текут одинаковые токи в противофазе. Их магнитные поля компенсируют друг друга, поэтому трансформатор ничего не делает. В силу симметрии цепи, на обоих концах R1 будет одинаковое напряжение. Значит, ток через него не потечет. Таким образом, входной сигнал был поровну разделен между двумя выходами. Делитель работает, как и положено делителю.

Для чего же тогда нужны трансформатор L4-L5 и резистор R1? А нужны они для изоляции портов out1 и out2, когда устройство используется, как сумматор. Допустим, сигнал подается на out1, а порты in и out2 нагружены на 50 Ом. Спрашивается, какой сигнал пойдет на out2?

Представим ненадолго, что точка out2 — это земля, и мы можем рассматривать L4-L5 как обычный трансформатор. Как мы выяснили выше, он нагружен примерно на 25 Ом. Поскольку L4-L5 является автотрансформатором с отношением числа витков первичной и вторичной обмотки 2:1, его входной импеданс составляет

100 Ом. Значение R1 выбрано таким же не случайно. Теперь вспомним, что out2 на самом деле не является землей. Но для нас это не так важно, поскольку любое изменение импеданса L4-L5 влечет за собой точно такое же изменение импеданса R1. Для нас важно лишь то, что их импедансы равны.

Выходит, что току нет особой разницы, куда течь из точки out1, в L4-L5, или в R1, и он делится поровну. Что же мы увидим в точке out2? Какой-то ток потечет через R1. Через L4 ток потечет такой же. Заметьте, что L4-L5 намотан так, что с L5 на out2 ток придет в противофазе относительно тока через резистор R1. В итоге токи компенсируют друг друга, и через R4 никакой ток не пойдет.

Токи на out1 и выходе трансформатора L4-L5 равны. Но ток с трансформатора идет на нагрузку 25 Ом, в два раза меньше. Это означает, что в режиме сумматора мы теряем половину мощности, или 3 dB.

В качестве домашнего задания предлагаю вам поиграться с приведенной схемой в LTspice и убедиться, что она действительно работает так, как описано выше. Схему вы найдете в этом архиве.

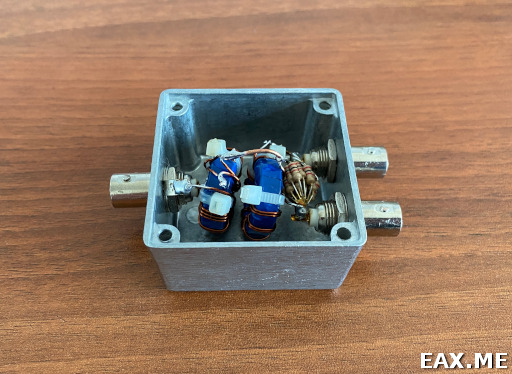

Практика

Трансформаторы были намотаны эмалированной проволокой диаметром 0.6 мм на ферритовых кольцах FT82-61. Трансформатор L1-L3 мотается трифилярной обмоткой, а L4-L5 — бифилярной. Я мотал по 8 витков в каждом, это около 25 см проволоки (с запасом). Измеренная индуктивность катушек при этом составила 5.6 мкГн. Это значение я и использовал в модели. Резистор R1 был сделан из 20-и резисторов 0.25 Вт номиналами 2 кОм, соединенных параллельно. Точное сопротивление получилось 98.3 Ом. С помощью антенного анализатора я убедился, что резистор не проявляет реактивных свойств на частотах до 30 МГц.

Все это хозяйство было помещено в небольшой металлический корпус:

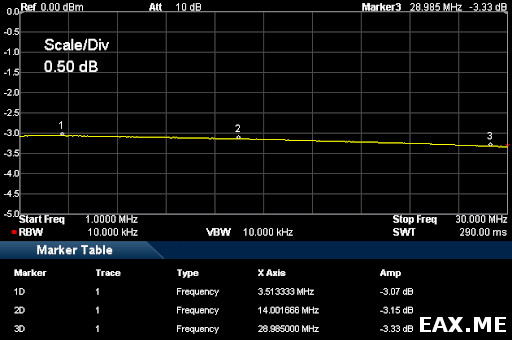

Для проверки делителя был использован анализатор спектра:

Здесь сигнал следящего генератора был подан на порт in, а на скриншоте мы видим выход с out1. Порт out2 при этом был нагружен на 50 Ом. Видим, что сигнал делится между портами поровну (-3 dB) за минусом небольших потерь.

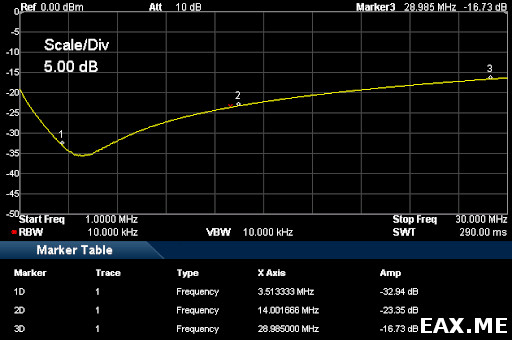

Определим изоляцию портов out1 и out2:

В интересующем интервале частот в худшем случае видим -16.7 dB.

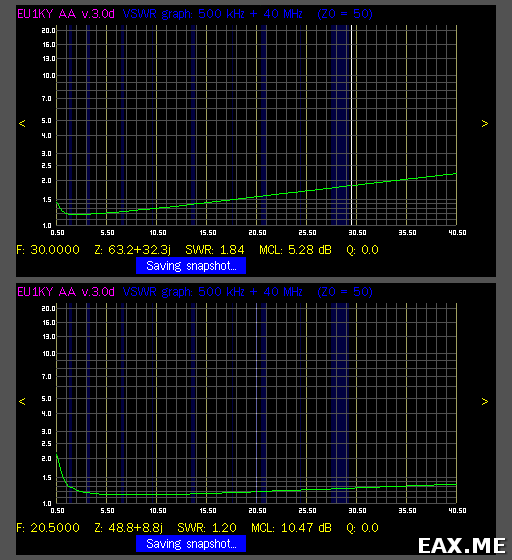

Также проверим КСВ в режиме делителя и сумматора:

В любом режиме КСВ не превышает 1.85 на всем интервале 1-30 МГц. То есть, в худшем случае отражается около 8% мощности.

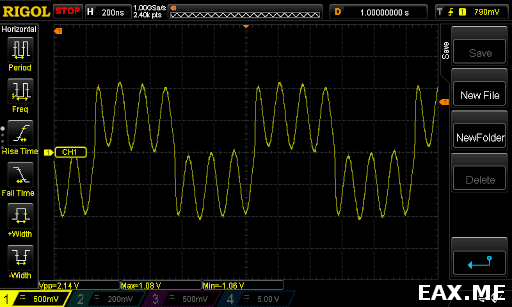

Наконец, убедимся в работе сумматора при помощи генератора сигналов и осциллографа:

Перед нами сумма меандра с частотой 1 МГц и синусоиды с частотой 7 МГц. Роботу устройства в режиме делителя таким образом тоже можно проверить. Но картинки при этом выходят скучные, поэтому здесь я их не привожу. Можно разве что убедится, что сигнал на out1 и out2 имеют одинаковую фазу, как это предсказывал LTspice.

Заключение

Описанный делитель/сумматор можно сделать за один вечер. Заинтересованным читателям предлагается повторить его на каких-нибудь других ферритовых кольцах и/или с другими числом витков, после чего поделиться результатами в комментариях.

Возможно, вас заинтересуют предыдущие статьи, в которых поднимались темы согласования импеданса, работы трансформаторов, и всякого такого:

А на этом у меня все. Как обычно, буду рад вашим вопросам и дополнениям.

Дополнение: Еще вас может заинтересовать статья Несколько способов сдвинуть фазу ВЧ сигнала, особенно описание квадратурного гибридного ответвителя из нее. См также Самодельный делитель/сумматор на частоты до 500 МГц на базе ADP-2-1W+ и Самодельный КСВ-мост и примеры его использования. Схема из последней статьи может быть использована в качестве делителя / сумматора 6 дБ. В заметке Безиндукционные резисторы и проекты на их основе приводится схема делителя / сумматора 6 дБ на резисторах.

Источник